# HEWLETT-PACKARDJOURNAL

# HEWLETT PACKARD JOURNAL

Technical Information from the Laboratories of Hewlett-Packard Company

#### JANUARY 1982 Volume 33 • Number 1

#### **Contents**:

Signal Processing Using Surface Acoustic Waves, by William R. Shreve Compact, rugged SAW devices that require no adjustment make real-time convolution, correlation, and dispersive filtering less difficult.

**Retrofitting for Signature Analysis Simplified, by Robert Rhodes-Burke** Signature analysis is a great help in troubleshooting digital products designed to use it, but what about all the products that aren't?

A Fast, Compact High-Quality Digital Display for Instrumentation Applications, by Kunio Hasebe, William R. Mason, and Thomas J. Zamborelli Why design a custom display when you can just plug one in? This one is easy for a microprocessor to talk to.

#### In this Issue:

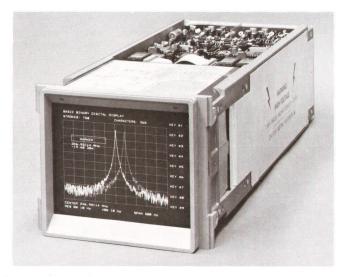

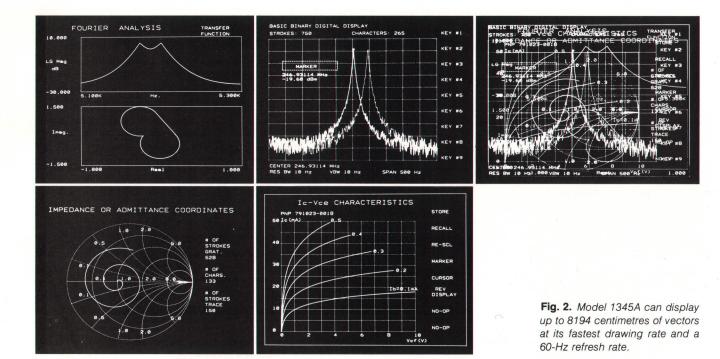

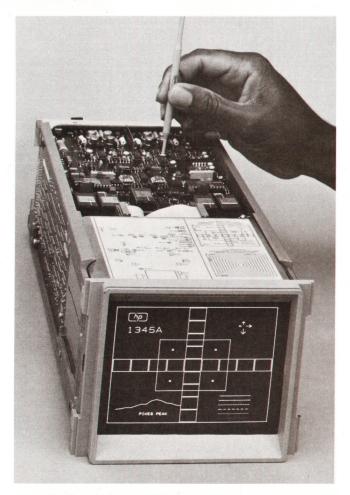

Electronic instruments and systems usually have a display of some kind to present data to humans in a readily understandable form. More and more, such systems have microcomputers inside, and while they may be fed continuously varying real-world quantities like voltages, speeds, and temperatures, the first thing they do with this analog data is convert it to binary numbers so that internally they can operate entirely digitally. This month's cover subject, the 1345A Graphics Display Module, is a high-quality cathode ray tube display that's designed to be built into spectrum analyzers, network analyzers, and other electronic instruments based on microcomputers. The 1345A is easy for a microcomputer to talk to, because it understands

picture descriptions in a simple binary language. With it, an instrument designer can provide high-quality graphics and text while avoiding the time and expense required to design a custom display. Among the 1345A's contributions are its speed, line quality, resolution, number of brightness levels, and compactness—the entire module is only a little larger than the CRT. It tests itself, too. The design story begins on page 20.

Complex digital systems, especially computers and microcomputer-based products, are particularly difficult to troubleshoot. If you connect an oscilloscope to any point in a digital circuit, you see a voltage switching rapidly between two levels. Without specialized test equipment and detailed knowledge of the system, it isn't possible to tell whether that "bit stream," as it's called, is correct. Yet it's impractical for every field service technician to have that kind of knowledge and equipment. Signature analysis was developed as a response to this problem. Guided by a test procedure, the technician probes points in the system and observes four letters and/or numbers (a signature) displayed by a compact instrument (a signature analyzer). Comparing these signatures with documented correct signatures tells at once whether things are as they should be. The catch is that the system has to be designed for this kind of troubleshooting so that when it's being tested, known bit streams can be introduced and the system can be set up so that signatures throughout it are predictable. But what about all the products that were designed without this capability? Can't they be retrofit for signature analysis? Yes, they can, but it's not easy; some redesign is usually necessary. Again a problem, and again a solution, the 5001A/B/C/D Microprocessor Exercisers. The four versions of this instrument make it easy to retrofit products based on four widely used microprocessors without costly redesign. How does it work? The story begins on page 9.

Last month's issue reported on HP developments in surface acoustic waves, or SAWs, and described SAW delay lines, filters, resonators, and sensors. In this issue, on page 3, you can read how SAWs can be used to do exotic signal processing, such as pulse compression, variable-bandwidth filtering, matched filtering, variable time delay, adaptive filtering, correlation, convolution, and Fourier transformation. Compared to digital processors that do the same things, SAW devices are small, simple, and rugged, operate in real time, and don't require high-accuracy analog-to-digital conversion. Their disadvantage is a limited dynamic range.

This month we're doing something we haven't done in our 32-year history. We're asking you, our readers, to tell us what you think of this publication. In the center of this issue we've put a reader opinion questionnaire. Please help us by completing it and mailing it back to us. If someone's already removed the questionnaire, your comments are welcome without it, now or at any time.

-R. P. Dolan

Editor, Richard P. Dolan • Associate Editor, Kenneth A. Shaw • Art Director, Photographer, Arvid A. Danielson • Illustrator, Nancy S. Vanderbloom Administrative Services, Typography, Anne S. LoPresti, Susan E. Wright • European Production Supervisor, Henk Van Lammeren

# Signal Processing Using Surface Acoustic Waves

If electrical signals are converted into minute acoustic waves on the surface of a piezoelectric crystal, the signals can be processed in novel ways for various electronic applications. Such devices are small, rugged, and can be fabricated using microelectronic techniques.

#### by William R. Shreve

**S** URFACE-ACOUSTIC-WAVE (SAW) devices can be used for analog signal processing other than basic filtering and frequency control.<sup>1</sup> By tailoring the characteristics of a device to a particular application's requirement, one can design systems to do pulse compression, variable-bandwidth filtering, matched filtering, variable time delay, adaptive filtering, correlation, convolution or Fourier transformation. The major advantages of SAW components are real-time processing, small size and simplicity. The disadvantage is a limited dynamic range. Digital systems performing the same operations are capable of greater flexibility and accuracy at the expense of increased processing time and the high precision of analog-to-digital (A-to-D) conversion required at the input.

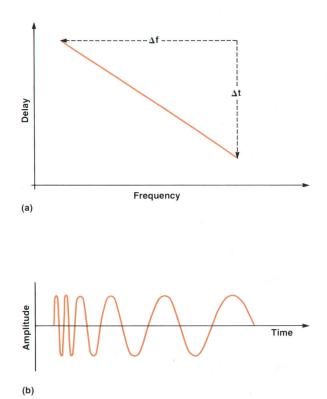

**Fig. 1.** (a) Delay characteristic of linearly dispersive (downchirp) filter. (b) Impulse response of same filter.

#### **Dispersive Delay Lines**

A number of signal processing functions can be performed with dispersive delay lines. A dispersive delay line is a filter whose delay is a function of the input frequency. Fig. 1 shows the characteristics of a linearly dispersive delay line or chirp filter. The different frequency components of a short-duration, broadband input pulse are spread out in time as they pass through the filter. This spreading causes a reduction in peak power. Conversely, an appropriately matched chirp (spread-frequency) input signal is compressed in time by the filter. This compression improves the signal-to-noise ratio and simultaneously reduces the duration of the signal.

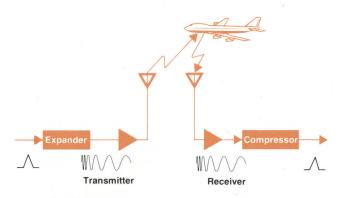

The first application of these devices was pulse compression for radar systems like that shown in Fig. 2.<sup>2</sup> An initial pulse is expanded in time, usually in a filter with a linear dispersion characteristic, amplified, and transmitted with all frequency components at the same power level to maximize the transmitted power. The received signal is compressed in another dispersive filter to enhance the signal-to-noise ratio. This system makes efficient use of transmitter power, increases the system's resolving capability in both range and velocity and reduces interference from other signals.

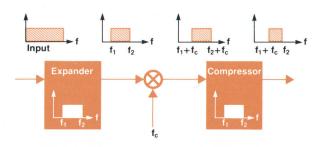

Chirp filters have also been used for variable-bandpass filters.<sup>3</sup> A pulse compressor and expander like those used in the radar system can be combined with a mixer as shown in Fig. 3. The passband of the system is determined by the overlap of the passbands of the two chirp filters and the relative offset is determined by the mixing frequency  $f_c$ .

Chirp filters can also be used to perform analog Fourier transform operations.<sup>4</sup> As shown in Fig. 4, the input signal is mixed with a chirp signal, passed through a matched chirp filter and postmultiplied by another chirp signal. Mathematically this can be expressed as follows:

$$\mathbf{F}(\mathbf{t}) = \left\{ \left[ \mathbf{S}(\mathbf{t}) \cdot \mathbf{C}_{1}(\mathbf{t}) \right] \ast \mathbf{C}_{3}(\mathbf{t}) \right\} \cdot \mathbf{C}_{2}(\mathbf{t}) \tag{1}$$

If S(t) is a bandlimited signal and  $C_1(t)$  and  $C_2(t)$  are identical constant-amplitude chirp signals matched to the uniform filter impulse response  $C_3(t)$ , then F(t) becomes

$$F(t) = \exp\left(j4\pi f_1 t\right) \int_{-\Delta t/2}^{\Delta t/2} S(t) \exp(-j2\pi f\tau) d\tau \qquad (2)$$

**Fig. 2.** SAW devices can be used in chirp radar systems by expanding a pulse before it is transmitted and compressing the received signal back into a narrow pulse so that distance accuracy is maintained. Expanding a pulse reduces the peak transmitter power required and pulse compression improves the signal-to-noise ratio in the receiver.

where  $f = (\Delta f / \Delta t)t$ ,  $\Delta t$  is the length of the mixing chirp signal  $C_1(t)$ , and  $f_1$  is the center frequency of that signal. This expression is the Fourier transform of the signal S(t) over the time interval  $\Delta t$ . For signals longer than  $\Delta t$ , the filter output from one  $\Delta t$  interval will interfere with the output from the next interval. Therefore, two channels would be required in parallel with appropriate switching for continuous transformation. The signal bandwidth must be limited to the difference between the filter bandwidth and the mixing chirp signal bandwidth. The circuit shown in Fig. 4 is significant because it can be used as a real-time equivalent of the digital Fourier transform to do spectrum analysis, convolution, or correlation. SAW devices can be used for the chirp filter and to generate the mixing chirp signals. Signal processing system capabilities depend on filters with large dispersion time and large bandwidth because these two parameters determine the maximum data rate and dynamic range of a system.

The accessibility of surface waves and their nondispersive propagation characteristics make chirp-filter design straightforward. Controlled variation of delay as a function of frequency is accomplished by choosing the appropriate transducer electrode pattern.

In SAW devices, the delay is proportional to the length of the propagation path, which in turn is determined by the distance between the input and output transducers. The frequency of the wave launched by a transducer is determined by the electrode spacing. Hence, frequency and

**Fig. 3.** SAW chirp filters can be used for variable bandwidth filters as shown in the simple block diagram above. As the mixing frequency  $f_c$  increases the output bandwidth narrows.

**Fig. 4.** Chirp filter implementation of analog Fourier transform. Chirps  $C_1(t)$  and  $C_2(t)$  can be generated by pulsing SAW chirp filters. The output F(t) is the Fourier transform of the signal S(t).

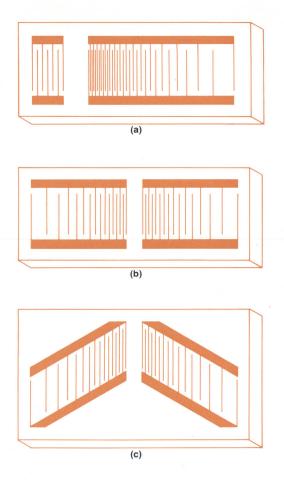

delay can be changed and controlled by the size and spacing of the transducers. Three transducer designs (Fig. 5) have been used for dispersive delay lines.<sup>5</sup> One uses a single, long dispersive transducer with a short, nondispersive, broadband transducer as the other port (Fig. 5a). This technique requires weighting\* of only one transducer and is therefore the most straightforward and most easily analyzed. It has the disadvantage that it is difficult to match the nondispersive transducer over a broad frequency range

\*Here weighting is the variation of the lengths of the electrode fingers in a transducer to achieve a desired impulse response.

**Fig. 5.** Three SAW transducer configurations used to make dispersive (chirp) filters. (a) Broadband, nondispersive transducer on the right, dispersive transducer on the left. (b) Both transducers are dispersive and shorter than the long one in (a). (c) Slanted arrangement of transducers used in (b). This minimizes distortion caused by propagation under transducer electrodes.

**Fig. 6.** Reflective array compressor. Here two broadband transducers are used for the input and output and dispersion is obtained from the variation in path length for different frequencies. The wave is reflected when the spacing in the direction of propagation is a wavelength  $\lambda$  (the period for adjacent grooves in the grating is about  $\lambda/\sqrt{2}$ ).

and still achieve low insertion loss.

In the configuration of Fig. 5b, two transducers are used to achieve the dispersive characteristic. Each transducer contains fewer fingers than the one dispersive transducer in the configuration of Fig. 5a and is therefore easier to match. A broadband nondispersive transducer is not required. The resulting filter will have lower loss, but the design and analysis, if both transducers are weighted, is more complex because the time response of the filter is the convolution of the impulse responses of the two transducers. Both of these designs require compensation for effective velocity changes under the transducer that are introduced in fabrication, for propagation losses and dispersion introduced by the electrode metal, and for scattering losses as the waves propagate under the transducer. These scattering losses are particularly severe in compression (up-chirp) filters where the high-frequency components of the signal must propagate under the low-frequency part of the transducer. Since plate-mode (or bulk-wave) velocities are higher than surface-wave velocities, the low-frequency electrodes can scatter higher-frequency surface waves synchronously into plate modes. This scattering increases insertion loss and causes spurious output signals.

These problems are eliminated in the slanted design shown in Fig. 5c. The propagation direction is the same as in the other designs. At high frequencies, surface waves are launched only at the top of the device. At low frequencies, waves are launched only at the bottom. This configuration eliminates propagation under large numbers of nonsynchronous electrodes and thereby reduces dispersion, attenuation and scattering effects. The impulse response is a somewhat complicated convolution of portions of the impulse responses of the two transducers. This complication makes precise analysis difficult, but the slanted structure eliminates the Fresnel ripple that is characteristic of transversal dispersive delay lines.

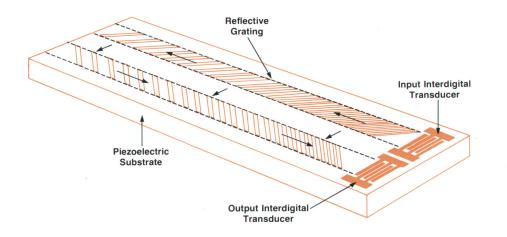

Another approach to dispersive delay lines is shown in Fig. 6. The reflective-array compressor (RAC) uses reflection of surface waves to achieve varying path length.<sup>6</sup> The reflection arrays consist of grooves whose reflectivity is varied by controlling their depth as a function of position along the array. Waves at all frequencies are launched by a single broadband transducer and reflected at right angles by the first reflection array at the point where the spacing of the grooves along the direction of propagation is a wavelength.

As shown in Fig. 6, a second array reflects the wave back to the output transducer. The advantages of this configuration are large dispersion, since the length of the device is used twice, and very low distortion, since reflective arrays introduce minimal distortion as the surface waves propagate through them. The disadvantage is more complicated fabrication.

The RAC device has been extensively used in systems requiring large dispersion times or large bandwidths. Laboratory devices have been built with a 500-MHz bandwidth and 10  $\mu$ s of dispersion.<sup>6</sup> Other devices have been built with up to 100  $\mu$ s of dispersion, but lower bandwidths.

#### **Fixed Correlators**

Chirp devices are examples of matched filters designed to detect particular frequency modulated signals. They are

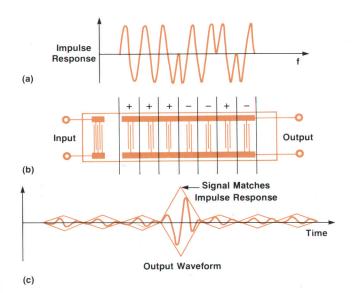

**Fig. 7.** SAW implementation of a seven-bit biphase-code correlator. An incoming signal is converted into a surface acoustic wave by the input transducer in (b) and propagates toward the output transducer. When the shape of the surface wave under the output transducer matches the impulse response of the transducer (a), a correlation pulse occurs at that time in the output waveform (c).

well suited to radar applications because the compressed pulse output is insensitive to Doppler shifts at the input and has low time sidelobes. In other applications where Doppler shift is not a problem, amplitude- and phasemodulated codes are appropriate. These fixed-code correlators can be implemented easily with tapped SAW delay lines.<sup>7</sup> The size of a tap (or set of electrodes) determines its amplitude and its position determines its phase. To match a known coded input, the impulse response of the SAW device is the time inverse of the waveform.

Fig. 7 shows the surface-acoustic-wave implementation of a seven-bit biphase-code correlator. The electrode connections to the summing bars determine the phase of the uniformly spaced taps. In practical systems, many other codes besides seven-bit codes are used. As the number of taps increases, performance is degraded by the attenuation caused by scattering, and by spurious signals generated by reflection. This distortion can be reduced by slanting the tapped transducer in a manner similar to that discussed for the chirp transducer (Fig. 5c). In this case, however, the energy is launched across the entire width of the device and the part of the beam intersected by an individual tap (electrode pair) affects the tap weight.

Multiphase codes can be used to advantage in communication systems to reduce multipath sensitivity. These systems are called spread-spectrum systems because the information is transmitted over a larger bandwidth than that required for the data itself. If r is the data rate and there are n taps per bit of information, then the code bandwidth is n times r. This seems to be an inefficient use of the spectrum, but since the matched filter discriminates against other signals, it should be possible to have multiple signals with differing codes share the same portion of the spectrum. The major advantage of spread-spectrum systems is the reduced sensitivity to interference from signals reaching the receiver by different paths. In a narrowband transmission system this can lead to cancellation and loss of the incoming signal. In a broadband system the signal level will be reduced, but the signal will not be lost.

The advantage of SAW devices as correlators is that they are passive, inherently synchronized, real-time processors. Digital correlators have to perform many multiplications and summations to determine when an input signal is present. To maintain synchronization, a preamble must be added to each transmission. This effectively reduces the data rate. With a SAW device this preamble can be very short if it is required at all. The radio data link described in the box on the next page is an example of a system that uses SAW devices in this manner.

Fig. 8. Basic configuration for SAW elastic convolver.

Fig. 9. Configuration of a monolithic diode storage correlator.

#### **Programmable Correlators and Convolvers**

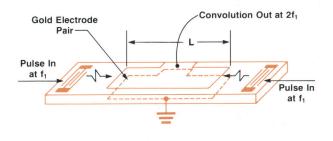

The disadvantage of fixed correlators is that the code can be changed only by making a new device. If nonlinear devices are used, it is possible to make programmable correlators where the reference function encoded in the transducer is determined by an auxiliary input signal. The simplest implementation of this device is the SAW elastic convolver (Fig. 8).<sup>8</sup> As the reference and the input signals pass through each other, nonlinearities in the substrate generate a signal that is proportional to the product of the signals. The sum-frequency component of this product has no spatial variation and can therefore be summed by a simple solid plane electrode. This summation corresponds to an integration of the product over the length of the electrode. Mathematically this is a convolution. If the reference signal is the time inverse of a signal to be matched, the output is the autocorrelation function of that signal. Therefore, if the reference is a chirp signal, the device can be used as a pulse compressor. If the reference is a coded waveform, it behaves like a fixed correlator. The advantage of a device with this flexibility is obvious-one device can now perform a variety of functions. The disadvantages are the requirement of generating a reference signal at each convolution interval and the inefficiency that results from relying on the weak nonlinearities in the substrate to obtain the product. The fact that the reference is also a moving wave makes signal acquisition and synchronization more difficult.

The weak nonlinearity problem can be solved by introducing a semiconducting medium to do the mixing.<sup>9</sup> This was first done by placing a semiconducting slab in close proximity to the piezoelectric substrate. The electric fields associated with the acoustic waves extend above the piezoelectric surface and modulate carriers in the semiconductor. The voltage generated across the thickness of the semiconductor is proportional to the square of the driving electric fields, so one component of this voltage corresponds to the product of the modulation of the two input waves. The interaction in this case is much stronger than the interaction in the piezoelectric substrate. It is highly dependent on the strength of the fields at the semiconductor surface and therefore on the size of the piezoelectric-tosemiconductor gap. The interaction strength is maximized with a gap of 100 to 500 nm depending on the semiconductor properties. The size of the gap is critical because contact between the two materials results in damping and scatter-

## **Radio Data Link**

The radio data link described here is a system for wireless data communications between a computer and several remote terminals located within a large, open building.<sup>1</sup> The system uses direct-sequence spread-spectrum techniques to overcome multipath interference and a SAW correlator to minimize sensitivity to signal variations and to improve signal acquisition time. This radio data communications system is designed to operate indoors over a limited range and with very low transmitted power. Such a system has two advantages over networks that use metallic or fiber-optic cables:

- A terminal may be installed wherever it is needed by putting it in a convenient place and turning it on. The need for cable installation to every foreseeable location is avoided.

- Terminals can be completely mobile and still remain connected to the network.

These two advantages make possible a variety of applications in office, warehousing, manufacturing, and instrumentation environments.

To realize these advantages fully, one must first address and overcome the problem of multipath interference. The potential for multipath interference arises when radio signals, as a result of reflections from the walls and objects within a building, reach a receiver by two or more paths of different lengths. Depending on their frequencies and relative path lengths, signals arriving by these paths may add destructively and produce deep nulls in the signal power available to a receiver. A conventional narrowband signal can suffer a loss greater than 25 dB. To overcome this loss either the transmitted power or the transmitted bandwidth can be increased. In either case more signal power reaches the receiver, but the wideband approach requires far less transmitted power for a given operating range. The system reported here uses a wide bandwidth developed by means of direct-sequence spread-spectrum techniques, sometimes called pseudo-noise or PN spread-spectrum.

To test the feasibility of using direct-sequence spreadspectrum techniques for data transmissions within buildings, three transceivers having the following characteristics were designed and built.

| Data Rate:         | 100 kilobaud              |

|--------------------|---------------------------|

| Code Length:       | 255 bytes                 |

| Code Rate:         | 25.5 MHz                  |

| Carrier Frequency: | 1.5 GHz                   |

| Modulation:        | binary phase-shift keying |

| Bandwidth:         | 51 MHz                    |

|                    |                           |

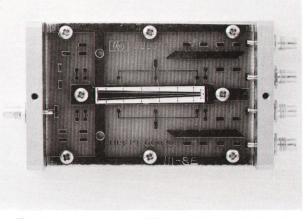

**Fig. 1.** Photograph of the SAW correlator portion of the radio data link before discrete components are bonded on.

Transmit Power: Operating Range: 5 milliwatts 300 metres

The operating range is adequate for many applications but can be increased by increasing transmitter power. For example, a range of approximately one kilometre can be expected with a transmitter power of 50 milliwatts.

Two CRT terminals and a central computer were outfitted with the transceivers. A multipoint polling protocol which used existing CPU software and terminal firmware was chosen in the interest of expediency. The transceivers were equipped with RS-232-C interfaces and appeared to the CPU and terminals as standard, high-speed, synchronous modems.

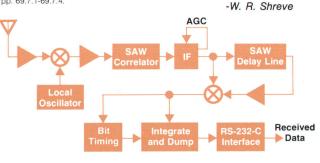

Although a microprocessor-based receiver was originally used in the system, it was replaced by a SAW-based receiver to overcome two major drawbacks. First, the microprocessor receiver was sensitive to rapid changes in multipath structure which sometimes occurred as people or objects moved about in the area where the radios were operating. Second, the microprocessor synchronism acquisition time was 100 milliseconds which severely degraded the channel throughput. These drawbacks were eliminated and a simpler block diagram resulted from the use of a SAW correlator (Fig. 1) in the receiver (Fig. 2). The incoming data is translated to the 350-MHz IF and decoded by the correlator. The data is differentially phase-shift keyed and is therefore contained in the relative phases of the compressed pulses at the correlator output. A second SAW device, a delay line with a delay of precisely one bit period, is used to achieve differentially coherent detection. A vital feature of the delay line detector is its ability to demodulate signals arriving via different paths properly even though their carrier phases are unrelated. The output of the detector is integrated during a 2-µs-wide window centered on the correlation peaks. In this way the receiver collects power from all signal paths and bases its data-bit decisions on total signal power rather than on the power from any single fragile path.

Signal acquisition time is limited by the settling time of the AGC loop to about one millisecond, which is considered adequate for the polled, two-terminal network. The polling rate is about 50 transactions per second. Reducing the acquisition time would not increase this rate appreciably. The SAW correlator results in a reduction in the signal acquisition time by a factor of 100 and thereby allows the system to operate at its full 100 kilobaud data rate.

#### **Acknowledgments**

This radio link was designed and built by Payne Freret, Ralph Eschenbach, Dick Crawford, Paul Braisted and Lyman Miller with the assistance of Zvonko Fazarinc, Hap Horn, and Frank Lee.

#### Reference

1. For a more detailed description of this system refer to P. Freret, R. Eschenbach, D. Crawford and P. Braisted, "Applications of Spread-Spectrum Radio to Wireless Terminal Communications," IEEE National Telecommunications Conference Record, 1980, pp. 69, 71-69.7.4,

**Fig. 2.** Simplified block diagram for the SAW-based receiver used in the radio data link.

ing of the waves. Too large a gap or variations in the gap causes decoupling or variations in the coupling between the piezoelectric substrate and the semiconductor.

Substitution of a diode array for the semiconducting slab further enhances the convolver's performance and flexibility because charge can be stored in the diode array. In one mode of operation, successive convolution outputs can be added to the charge stored in the diodes to make an integrating correlator. In the normal convolution mode, the reference signal can be stored as a charge image on the diodes to alleviate the problems of continual reference generation and synchronization with a moving reference. The storage time is determined by the diodes and is typically a few milliseconds. The reference must still be refreshed, but 1000 times less often.

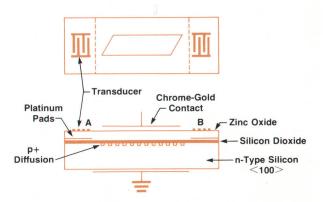

The difficulties in fabricating a two-substrate piezoelectric-semiconductor convolver can be bypassed by using a substrate such as gallium arsenide that is both piezoelectric and semiconducting or by depositing a thin layer of a piezoelectric material like zinc oxide on a semiconducting substrate like silicon (Fig. 9). Monolithic devices now have efficiencies and bandwidths equivalent to those obtained with separate substrates.<sup>10</sup>

The use of programmable SAW correlators and convolvers is currently limited to research laboratories. System applications are limited by the correlator's high loss and limited dynamic range. When the losses associated with transduction over a useful bandwidth (25%), propagation, and the interaction are combined, the ratio of the output power to the product of the two input powers is about -50 dBm. Thus if a +20 dBm reference is used, the ratio of signal-to-output power is -30 dB. This loss is more than 20 dB better than the first convolver loss reported, but it is still substantial. The dynamic range is limited by thermal noise at low power and saturation at high power and varies from 20 dB to 40 dB depending on the configuration. It limits both the useful power range at the input and the accuracy that can be achieved in the convolved output.

#### Summary

Surface wave technology is maturing and devices that were once confined to military applications demanding high performance, even though the cost may be high, are now being used in cost-sensitive commercial applications like television IF sections. Applications outside the military arena have been limited to simple filters and resonators. As commercial communication systems proliferate and become more complex, signal processing applications of SAW devices are becoming more common.

#### References

1. Hewlett-Packard Journal, Vol. 32, no. 12, December 1981.

2. J.R. Klauder, A.C. Price, S. Darlington and W.J. Albersheim, "The Theory and Design of Chirp Radars," Bell System Technical Journal, Vol. 30, July 1960, pp. 745-808.

3. V.S. Dolat and R.C. Williamson, "A Continuously Variable Delay-Line System," IEEE Ultrasonics Symposium Proceedings, September 1976, pp. 419-423.

M.A. Jack, P.M. Grant and J.H. Collins, "The Theory, Design, and Application of Surface Acoustic Wave Fourier-Transform Processors," Proceedings of the IEEE, Vol. 68, April 1980, pp. 450-468.

J.D. Maines, G.L. Moule, N.R. Ogg and G. Rich, "Improvements in Surface-Acoustic-Wave Pulse-Compression Filters," Electronics Letters, Vol. 9, April 1973, pp. 156-157.

6. R.C. Williamson and H.I. Smith, "The Use of Surface-Elastic-Wave Reflection Gratings in Large Time-Bandwidth Pulse-Compression Filters," IEEE Transactions on Microwave Theory & Techniques, Vol. MTT-21, April 1973, pp. 195-204. Also see references 11 and 12 below.

7. D.T. Bell, Jr. and L.T. Claiborne, "Phase Code Generators and Correlators," in Surface Wave Filters, H. Matthews, editor, John Wiley & Sons, New York, 1977, pp. 307-346.

8. A number of recent articles on elastic convolvers and references to earlier work can be found in the IEEE Ultrasonics Symposium Proceedings, November 1980, pp. 1-87.

9. G.S. Kino, "Acoustoelectric Interactions in Acoustic-Surfacewave Devices," Proceedings of the IEEE, Vol. 64, May 1976, pp. 724-748.

10. J.E. Bowers, B.J. Khuri-Yakub and G.S. Kino, "Monolithic Surface Wave Storage Correlators and Convolvers," IEEE Ultrasonics Symposium Proceedings, November 1980, pp. 118-123.

11. R.C. Williamson, V.S. Dolat, and H.I. Smith, "L-Band Reflective-Array Compressor with a Compression Ratio of 5120," IEEE Ultrasonics Symposium Proceedings, November 1973, pp. 490-493. 12. V.S. Dolat and R.C. Williamson, "BGO Reflective-Array Compressor (RAC) with 125  $\mu$ s of Dispersion," IEEE Ultrasonics Symposium Proceedings, September 1975, pp. 390-394.

#### William R. Shreve

Bill Shreve was born in Dobbs Ferry, New York and attended Cornell University, earning a BS degree in engineering physics in 1969. He continued his studies at Stanford University, receiving the MS (1971) and PhD (1974) degrees in applied physics. Bill joined HP in 1978 with four years of industrial experience working with SAW technology. At HP he has worked on SAW resonators and is the project manager for the SAW program at HP Laboratories. He is named as an inventor on three SAW device patents and is an author of more than twenty papers related to

SAW devices. Once an instructor in the Continuing Engineering Education Program at George Washington University, Bill is the founder and vice-chairman of the Santa Clara Valley Sonics & Ultrasonics Chapter of the IEEE and a member of the IEEE Sonics & Ultrasonics Group Administrative Committee. He lives in Sunnyvale, California with his wife, two daughters, and the family dog. He enjoys jogging, hiking, woodworking, and gardening.

# Retrofitting for Signature Analysis Simplified

This microprocessor exerciser provides preprogrammed external stimulus routines and monitoring circuits for signature analysis troubleshooting of microprocessorbased systems.

#### by Robert Rhodes-Burke

IGNATURE ANALYSIS troubleshooting techniques have reduced the cost of fault isolation in digital circuits for many HP customers. The cost savings have accrued from the use of lower-cost equipment and personnel with lower skill levels, and from more rapid fault isolation. Over 1000 companies have purchased HP signature analyzers for testing digital logic circuits.

Signature analysis testing is used often in complex digital systems. It is frequently designed into the products, but several cases of retrofit have been successful in products not designed originally with signature analysis in mind. In general, the most effective implementations are those where some thought was given to testability considerations in the product development cycle.

Until now, existing products not designed with signature analysis in mind were not retrofitted as often as they could have been. One factor may have been the perception by production and service engineers that the retrofit process

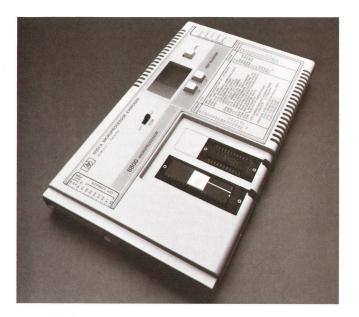

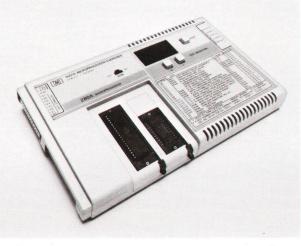

**Fig. 1.** Model 5001 A Microprocessor Exerciser makes it possible to apply signature analysis troubleshooting techniques to 6800-microprocessor-based products not originally designed for signature analysis methods. Other versions (5001B,C,D) test products based on the 6802/6808, 8085A, and Z80A microprocessors.

was similar to the design process and required R&D involvement. Designers are not always available to work on products already released to production, and production and service engineers may feel that they do not have the time or circuit familiarity to retrofit the product themselves. Consequently some products miss the opportunity to use this technique to enhance their serviceability.

Another point is that some minimal amount of hardware may be required to provide the timing signals to the signature analyzer. The signals required are simple in nature: start and stop flags to identify the boundary of the data stream of interest, and a clock pulse that indicates when data is valid for sampling purposes. Usually the designer can locate suitable timing signals already existing in the system. Occasionally a slight design modification, costing only a package of gates, is required. This represents some change, which can be considered intolerable in products released to manufacturing.

Thus the design-in philosophy is clearly the best, but the simplicity of the retrofit task, when viewed correctly, has not been stated strongly enough. The HP Model 5001A Microprocessor Exerciser (Fig. 1) should help remove some of the obstacles to evaluating signature analysis as a viable test alternative.

#### The Microprocessor Exerciser

The 5001A Exerciser makes the retrofit of signature analysis easier. The hardware impact on a product is reduced to the addition of a socket at the microprocessor location if one is not already present. The microprocessor exerciser provides a number of general-purpose preprogrammed stimulus exercises. These exercises can be adapted to a typical system with little effort. Valuable ROM space is not needed because the exerciser, acting as an external test stimulus, does not require any memory allocation concessions in the user system.

The exerciser provides signature analysis experience in products as the technique is learned. Users can begin immediately to use signature analysis in their product by connecting the exerciser to the product and selecting any of the preprogrammed stimulus programs. Thus the newcomer can actually experience the use of signature analysis before gaining an in-depth understanding of the process. Even if the user abandons the exerciser later to implement a designed-in approach, the user will benefit from the use of the exerciser and learn more quickly than by earlier methods.

The 5001A reduces the need for R&D personnel to be involved in the retrofit of existing products. Since the programs are preprogrammed and tested by the designers of the exerciser, the service engineer has a starting library of many routines useful in exercising circuits connected to microprocessor system buses. The exerciser lets the service engineer extend the programs to cover custom circuits or unique configurations in the product under test. The ability to write functional tests is also provided. These programs can be co-resident with diagnostic signature analysis exercise programs.

Additional product hardware requirements are nearly eliminated, except for the required socket for the microprocessor and the breaking of feedback loops in the circuits beyond the processor buses. It is still true that, unless feedback loops are broken, signature analysis techniques have some difficulty in isolating a fault. However, it should be noted that the detection of a fault is not impaired. Also, this deficiency affects most board testers, which observe only edge-connector activity. Good design practices can alleviate the grief caused by this configuration, at low expense to the product, whether tested on an automatic test system or on a bench using signature analysis.

Signature analysis takes place at the normal speed of operation of the system. This is a major contribution because faults that may not show up in slower-speed test methods can be detected by at-speed testing. The fact that the testing occurs in the product rather than on some fixture adds to the near-perfect duplication of the environment that will be seen by the circuit in normal operation. This benefit is not often realized in other test methods.

A number of preprogrammed test programs are carefully developed to take advantage of other features of the 5001A. An example is the bus signature test that produces a single-measurement result in response to the eight-bit bus activity. The most frequent application of this test is the single-measurement verification of a product's ROM data.

The 5001A Microprocessor Exerciser is the first of a family of exercisers for the most popular microprocessors (see page 17). The characteristics of other exercisers in this family are essentially the same as described for the 5001A, which is specifically designed for the 6800 microprocessor. Some of the features of these exercisers are:

Timing signals. All necessary timing and control signals required for a signature analyzer are produced within the circuits of the exerciser. This eliminates hardware overhead in the product under test. The timing signals are controlled by the program, whether internal or custom. This allows several programs to use dynamically varied stimulus depending upon the response of the product under test.

### **Signature Analysis Reviewed**

In signature analysis testing, the objective is the detection and isolation of digital faults that produce incorrect circuit functions. The technique requires a repeatable stimulus of the circuit so that digital data streams are produced at various points of interconnection (nodes) within the circuit. The signature analysis test collects these bit streams in a fashion that compresses them. The compression is similar to the well-known technique of cyclic redundancy checking in data communications. The results of this compression by HP signature analyzers are signatures consisting of four hexadecimal digits. In a properly operating circuit, the signature for a given node and a given stimulus is stable and predictable.

Because signature analysis is a stimulus and response technique, effective stimulus and response-measuring instruments are required to test a given circuit or system. For response, either the HP Model 5004A Signature Analyzer or the Model 5005A Signature Multimeter provides the required measurement capability. With stimulus applied to a circuit the user probes the nodes of the circuit with one of these analyzers and compares the signatures they display with those of a known good circuit, as listed in a service manual.

An important characteristic is that testing takes place within the product, at the normal speed of operation of the circuits, unlike most board test systems. To achieve this, the product, if microprocessor based, must execute software so that the stimulus process results from the program activity. The advantage of testing at speed is obvious, but blunted somewhat by the necessity of having a subset of the circuits functional before the test can take place. This subset is often referred to as the kernel. This is the innermost layer of hardware and/or firmware required to validate the basic function of the microprocessor chip. This is often the microprocessor and its requisite clocks and power supplies.

The signature analysis test is often viewed as a diagnostic test

that is used to isolate faults detected by some other means. Sometimes these means are functional or self-tests. In some implementations these means can be carefully designed signature analysis exercises that produce a go/no-go result.

The stimulus must be such that each node has a unique bit stream, and further, that the circuit elements are exercised so that the activity is an approximation of normal operation. This latter condition suggests that it is not necessary to generate all possible input states to exercise a digital circuit if certain conditions are never possible in the system. In any case the stimulus must be constructed so that a repeatable and continuous exercise of the circuits under test is provided.

Only if the stimulus is correct can the response of the circuits under test be evaluated as to its correctness. There is a simple dichotomy in the result, either the data stream was correct and produced a correct signature, or the signature was not correct. The latter case suggests a faulty data stream, and thereby detects a faulty function somewhere upstream of the data flow.

The stimulus is most often done by specially developed microprocessor programs that are executed in the product at the time of diagnosis. The stimulus programs are loops that cause repeatable digital data streams. This type of program is frequently an endless loop that exercises a functional block of circuits and then repeats. The technician or service person must be able to control the selection and initiation of these test loops so that appropriate exercises are used in the troubleshooting process. The service engineer who sets up the product for service documentation also must be able to influence the selection and effectiveness of these tests.

Timing information must be provided to indicate when the beginning and end of the test exercise occurs. Timing information is also required so that the data can be taken from the circuit under test only during the time when it is correct and stable.

- Built-in tests. Preprogrammed tests exercise the most commonly occurring elements in a microprocessor system. There are tests for ROM, RAM, and I/O devices. Several variations of the RAM and ROM tests are included to allow fault isolation to proceed quickly. Several functional tests are provided to allow singlemeasurement verification of major functional blocks.

- Simple to use. The user interface is very simple. Three pushbuttons control test selection and a slide switch controls the program source. The front panel reflects the nature of the exerciser with a summary of the tests and their access codes printed below the display. Connection to a product is straightforward and can be accomplished in seconds. Connection to the signature analyzer is likewise rapid, using only four wires that mate with the pod connectors of the HP analyzers.

- Test variety. Some tests are single-measurement functional tests, others are complete circuit exercisers. An example of a single-measurement test is the basepage RAM test, which produces a single signature that in the 5001A corresponds to the number of correctly functioning RAM locations in the 6800 basepage area. A complete circuit exercise is the output-port stimulus program which writes all possible patterns to any output port. The port is selected by connecting a sense line to its chip select or strobe. The program determines the location of the target port, and then exercises it exhaustively.

- Microprocessor test. A microprocessor instruction-set test is included that also cycles interrupts and verifies correct responses. The microprocessor exercise is automatically entered upon power-up so that the kernel of the product under test is validated. The test uses all but one instruction of the microprocessor, and tests each instruction for correct function. The hardware and software interrupts are also tested for correct operation. The result of the test is a single measurement which appears in the signature analyzer. A more complete test result can be achieved by probing every pin on the processor, because some pins are for outbound data or address only.

- User programmable. Users can easily supply external programs to customize the 5001A Microprocessor Exerciser to their applications. A socket is provided so that the service engineer can supply a 2048×8 EPROM containing custom test programs for a particular product. These tests can be a mixture of functional and diagnostic tests and can be selected easily in addition to the internal preprogrammed exercise programs.

- Bus signature tests. Tests are present that allow a single-measurement ROM verification independent of memory location or size. The use of the input qualifier line allows the user to execute a special bus signature program that allows data to be accepted only from locations that respond with the qualifier line in a specified state (0 or 1, depending on the test). By connecting the qualifier to a ROM chip select line, a ROM's data can be accessed regardless of its position in the memory space. This technique eliminates any need to learn the memory map of the product under test, which can be a time-consuming process. The data is processed inside the exerciser and fed serially out on a single pin in the TTL

output port of the exerciser. By connecting a signature analyzer to this pin, the entire contents of a ROM of an arbitrary size and position in memory can be verified. Each bit of the data is examined and contributes to the resulting signature. The single measurement is more effective than checksum methods frequently used in ROM verification. This approach can be very useful for products that use several ROMs as options. A single measurement can verify the presence or absence of a specific option in the product.

- External stimulus port. Not every point of interest in a circuit is always accessible to a microprocessor bus. This general-purpose stimulus port allows stimulus to be applied to such points. For example, this port might be connected to a keyboard input so that all possible keystrokes can be simulated by the exerciser while the microprocessor reads such inputs. A preprogrammed routine is provided to facilitate this type of test. Several variations on this exercise can be done when the qualifier line is used.

- Qualified stimulus programs. An external qualifier allows activity in the circuit under test to signal a dynamic modification of the stimulus. As described in the previous examples, an external qualifier input line is provided that facilitates testing when the exact addresses of certain devices are not known. In the bus signature example the qualifier line is used to find the ROMs of interest so that they may be tested. Custom programs can exploit this approach to produce dynamically alterable stimulus for portions of the circuits.

- Optimized for troubleshooting. The exerciser is optimized for troubleshooting digital circuits. The programs are carefully selected to provide a useful set of general-purpose routines to stimulate system components typically found in microprocessor systems. No keying in of programs or downloading is required to use the 5001A.

#### How the Exerciser Is Used

The 5001A is connected to the product under test by removing the microprocessor from its socket in the product. The processor is then placed in the 40-pin ZIF (zeroinsertion-force) socket on the exerciser. The flat cable from the exerciser is then connected to the vacant socket in the product. The signature analyzer is connected by placing the four wires from the timing pod of the analyzer in the connector at the right edge of the exerciser. The front panel of the signature analyzer is set up for the specified edge and polarity of the timing signals. The test setup is then complete (Fig. 2).

The user then applies power to the product under test, which also applies power to the exerciser. (The exerciser requires a maximum of 550 mA, nominal, at +5V.) The microprocessor test is selected automatically and executed after power-on. The user can place the data probe on a +5V line to verify the functionality of the processor.

The user can now call preprogrammed tests with a few keystrokes and execute the desired tests by pressing the **ENTER** button. The tests selected most frequently at poweron are the ROM and RAM tests. A convenient first test for the newcomer is the free-running address test. This places

**Fig. 2.** To use the 5001 A, the microprocessor in the product under test is removed from its socket and placed in the socket on the exerciser. The flat cable from the exerciser is connected to the vacant socket in the product. Four wires connect the exerciser to the signature analyzer, in this case the 5005A Signature Multimeter.

the address bus in all possible states and allows the user to validate the function of address decoding and buffers in the product.

Subsequent tests are easily selected from the exerciser front panel and executed. No restriction is made on the order of execution. Custom programs stored in EPROM or PROM also can be selected easily by the ROM-select slide switch on the front panel of the exerciser. This substitutes the external PROM for the internal ROM and allows the same degree of selection versatility.

The correct test program, of course, depends upon the product under test. There are over fifty preprogrammed stimulus programs, many of which are general-purpose. The sequence of tests should reflect the natural organization of the microcomputer portion of the product under test. The natural progression would be to start with the test of ROM either by selecting the address range appropriate to its addresses or by using the bus signature test. Then the RAM test could follow to validate system RAM. In this case either the basepage RAM test could be used or one of the half-dozen other RAM tests.

At this point it becomes more difficult to generalize about the appropriate test. Since each product has different I/O configurations, the next test selected will vary from product to product. The only general rule is to select tests that move the boundary between the known good (tested) circuitry and the unknown circuitry in a direction away from the processor bus. This corresponds roughly to the concept of "growing the kernel." Layers of tested circuits are added like the skin of an onion around the processor. The result is an increasing base of resources that can be used for test stimulus or response detection.

The I/O section can be tested to some degree by the general purpose I/O tests that are included in the 5001A Microprocessor Exerciser. There are two categories: outputport stimulus tests and input-port stimulus tests.

The execution of the selected program is straightforward—simply pressing the **ENTER** button on the exerciser will cause the program to be executed. That program will continue to execute until another program is selected and entered or power is removed. The program execution is sufficient to cause some stimulus to be generated in the product under test. The user then places a data probe on the devices being stimulated to collect data streams. The resulting data is compressed to produce a signature that can be read from the signature analyzer.

The user then compares that result to the documented result from a known good unit. The response is either correct or incorrect. A mismatch between the two readings indicates that at least some portion of the data stream in the product under test is not correct. The user then applies backtracing techniques to the circuit to locate the faulty component(s).

The test is only as good as the documentation developed by the service engineer. To develop effective documentation the service engineer must take the signature from a known good unit while it is being stimulated in the same fashion as will be used in the service environment. This is accomplished by the selection of an appropriate stimulus, application of the stimulus, and then documentation of the resulting signatures for later comparison with results from tested units.

The evaluation of a test is not finished until verification of the effectiveness of the test. This can be done by probing within a circuit in a known good unit while faults are induced. Should the test fail to detect an induced fault (such as a shorted trace) it should be analyzed to discover how it could be used better or modified to correct this deficiency. In most cases simple modifications can be made. A side effect, however, is that a new set of signatures will often result when a test program is modified.

The programs provided in the exerciser are generalpurpose and not always suitable for every application of a customer. An easy means is provided so that a custom program may be run on the exerciser. An extensive user guide has been developed for custom programming. Sample programs are provided along with short tutorials on program modifications. There also is a suggested programcontrol routine that can be placed in the custom ROM so that the custom-test selection process can be identical to the internal program ROM.

#### **Hardware Design**

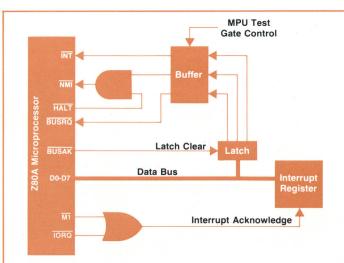

The microprocessor buses in the product under test and the exerciser are separated by buffers. This permits the detection and isolation of faults that affect address and data transfer in the product, while allowing the diagnostic pro-

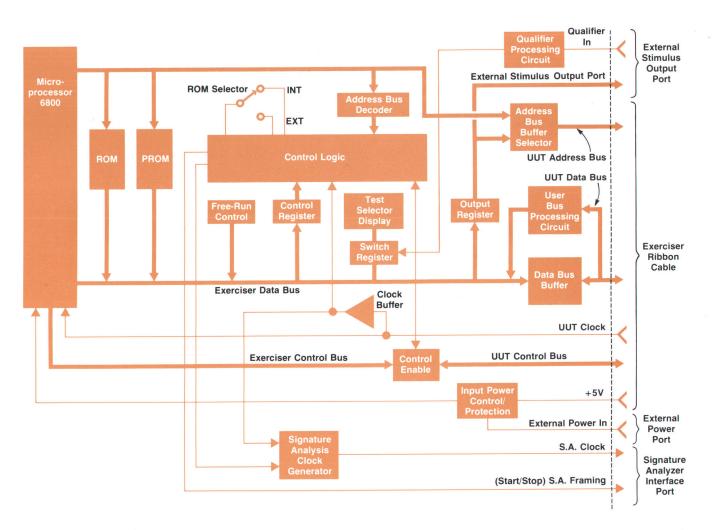

Fig. 3. Block diagram of 5001A Microprocessor Exerciser (UUT = unit under test).

gram to function normally. This would not be possible in some cases in which signature analysis has been designed into the product.

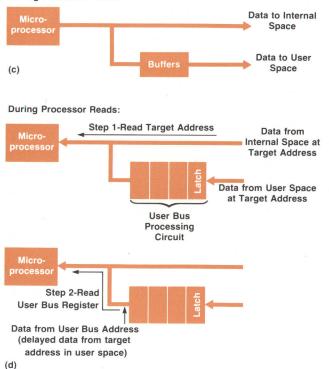

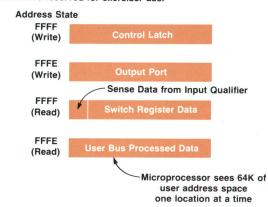

Fig. 3 shows a block diagram of the 5001A Microprocessor Exerciser. The user bus processing circuit can be used to monitor the data transactions in the product under test. Since simultaneous activity occurs in the exerciser and the product, it is useful to be able to capture the activity of the product data bus so that the microprocessor can, if the program is so written, test the data from the user system. The exerciser's novel data bus capture circuit allows dual address space maintenance (i.e., in the exerciser and the product) while access to data on the user's product data bus is maintained. A shift-register-like delay is introduced to capture and delay the user bus data for later access by the microprocessor. (See Fig. 4. Also see "Software Design," page 15.) Software control is maintained so that user data can be accessed or ignored at the program's option. This lets the processor access both the programs in the exerciser and the data stored in ROMs or RAMs in the product under test. The exerciser cannot, however, execute programs from the product being tested. This limitation is not serious because the programs can be validated by testing the machine code with the bus signature test. This test is not available in any signature analysis product at present. The operation of the unit in the presence of bus faults is also an improvement over earlier techniques.

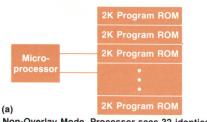

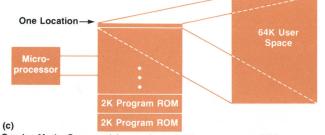

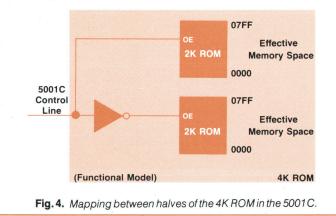

An internal 2K-byte program ROM contains the preprogrammed stimulus firmware. This ROM or the user's custom ROM can be selected from the front panel. The ROM is decoded in such a way that test programs can appear to run in any location in the possible 64K-byte address space of the processor (see "Software Design," page 15 and Fig. 5a).

There is a single sense line which is processed in a manner similiar to the data bus activity in the unit under test. This line can be connected anywhere in the user's system so that TTL-level activity can be captured synchronously with the stimulus program activity. A typical use of this external qualifier line is on chip-select lines, to identify interesting sections of the address map in the system under test.

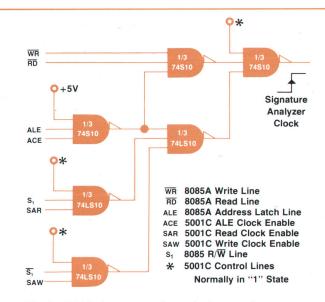

The signature analysis clock generator takes the clock signal from the processor and, after buffering in a highspeed buffer, generates a program-controlled signatureanalysis clock at either the read or the write time of the microprocessor. The programs for the exerciser use the software control feature to generate the qualified clocks sent to the signature analyzer for windowing a data stream.

The hardware generation of clocks ensures that the microprocessor is in step with the data being collected by the signature analyzer. Clock skew has been minimized by a

**During Processor Writes:**

**Fig. 4.** The 5001A maintains a dual 64K address space by mapping the user space in the product under test into a single location in its internal memory. The user bus processing circuit delays responses from the user memory and the micro-processor reads the delayed data by reading the single internal memory location.

compact low-power Schottky logic implementation, and produces negligible effects in most test systems. The fact that the signature analyzer is connected to the exerciser rather than the product under test eliminates the possibility of error due to incorrect connection and simplifies testing when several products must be checked. The single setup required for all built-in programs in the exerciser eliminates another source of operator error. Because custom programs can access all features of the hardware, this single setup feature is available even in custom programs.

The control logic allows the software to control the functions of the exerciser as the stimulus programs execute. An example is placing address buffers in the high-impedence state during the microprocessor test so that address or data bus faults in the system under test cannot affect the test. Other functions allow access to internal exerciser registers and the software-induced free-run of the processor.

In the exerciser is a simplified overlay register scheme that is software-controlled. The processor executes reads or writes to internal exerciser registers by reading or writing to two memory locations. Thus the overlay register scheme has minimal impact on the address space available for programs. Unlike some input checking equipment test alternatives, the complication of a movable shadow RAM effect is not present. The two locations of the 65,536-word memory that are affected were carefully chosen and can be disabled for testing the user's system if required.

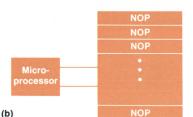

The user can make the processor free-run by executing a very short program that sets a bit in the control logic and latches the free-run state. As this occurs the internal ROM is disconnected and a CLR B instruction is connected in its place. CLR B is effectively a NOP instruction when observing processor activity externally (see Fig. 5b). For all possible addresses the processor sees an instruction whose outward effect is simply to increment the program counter and read (fetch) the next instruction (also a CLR B). The result is that the processor cycles through all possible addresses and reads continously. This is an exhaustive test of the address bus of the product under test.

Any of the 51 tests in the exerciser program memory may be selected by pressing two switches on the front panel. The value of the two digits displayed is available to the processor by reading a switch register. This is usually done only during the reset that occurs after the user presses the **ENTER** button to indicate that the selected test number is to be executed. Whenever the switch register is modified the decimal points in the display are lighted to indicate a possible mismatch between the test currently executing and the number in the display. This condition is cleared when the **ENTER** button is pressed.

The external output port is an eight-bit latch that can be accessed and updated at any time by the program. This port provides stimulus signals for circuits beyond the reach of the processor bus at a rate synchronous with the stimulus program. This allows testing some circuits that need initialization, require external inputs (such as keyboard), or run asynchronously with the microprocessor bus (such as the handshake line into a parallel interface device).

The exerciser requires that the product under test supply an additional 550 mA at 5Vdc  $\pm$  5%. If this cannot be provided through the microprocessor socket, the exerciser

# The First Hewlett-Packard Journal Reader Opinion Survey

#### Dear Reader:

We need your help in this, our first Hewlett-Packard Journal reader opinion survey. We want to know what you think about our publication.

Please take a few minutes to fill out the questionnaire below and mail it back to us. Feel free to add any comments you wish.

Your response is important, for without it we may never know how you feel about the Journal. Thanks for your help.

Richard P. Dolan, Editor

Please mail completed questionnaires to the address shown below for your location.

#### **United States of America**

Hewlett-Packard Journal Survey 1820 Embarcadero Road Palo Alto, California 94303

#### Canada

Hewlett-Packard Journal Survey 6877 Goreway Drive Mississauga, Ontario L4V 1M8 Canada

#### Japan

Hewlett-Packard Journal Survey Yokogawa-Hewlett-Packard, Ltd. 29-21 Takaido Higashi 3-Chome Suginami-Ku, Tokyo 168 Japan

#### Australia/New Zealand

Hewlett-Packard Journal Survey 31-41 Joseph Street Blackburn, Victoria 3130 Australia

#### All Other Areas:

Hewlett-Packard Journal Survey 1820 Embarcadero Road Palo Alto, California 94303 U.S.A.

#### QUESTIONNAIRE

- 1. For approximately how long have you received the HP Journal? (Circle one number)

- 1. Less than one year

- 1 year to 2 years

2 years to 3 years

- 4. 3 years to 4 years 5. 4 years to 5 years

- 6. more than 5 years

- 2. When you receive the HP Journal in the mail, how soon do you usually look at it? (Circle one number)

- 1. Upon receipt

- 2. Within a day

- 3. Within a week

- 3. How do you usually read the HP Journal? (Circle one number)

- 1. Just glance at it

- 2. Read it all briefly

- 3. Read some sections and not others

- 4. Read it all carefully

- 4. Where do you usually read the HP Journal? (Circle one number)

- 1. At home

- 2. At work

- 5. Most HP Journal articles are about product designs. Please circle the types of products that you usually read about. (Circle all appropriate)

- 1. Handheld calculators

- 2. Personal computers

- 3. Desktop computers

- 4. Computer systems

- 5. Computer peripherals

- 6. Computer software

- 7. Data acquisition and control products

- 3. Field service instruments

- 9. Laboratory instruments

- 10. Instrument systems

- 11. Logic and processor-based circuit analysis products

- 12. RF and microwave test equipment

- 13. Telecommunications test equipment

- 14. Analytical instruments

- 15. Medical instruments

- 16. Components

- Some HP Journal articles are not directly related to product designs. Please circle the types of HP Journal articles you usually read, including product design articles. (Circle all appropriate)

- 1. Product designs

- 2. Product applications

- 3. Semiconductor technology (e.g. SOS, NMOS, CMOS, GaAs)

- 4. Computer aided design

- 5. Fiber optics

- 6. Calculator algorithms

- 7. Reliability engineering

- 8. Viewpoints—personal opinions of HP experts

- 9. In-house HP technology (e.g. electron beam system)

- 10. Research reports (e.g., surface acoustic waves, laser technology, proximity effect)

- 11. Laboratory notebook

- 12. Software technology

- 13. Basic tutorial articles

- 14. In this Issue-editor's letter

- 15. Author biographies

- 7. Please tell us how much of the information in the HP Journal you find to be objective, accurate, and believable. (Circle one number)

- 1. All of it

- 2. Virtually all of it

- 3. Most of it

- 4. More than half of it

- 5. Less than half of it

- 8. When you are through with your copy of the HP Journal, what do you usually do with it? (Circle one number)

- 1. Toss it away

- 2. File it

- 3. Pass it along

9. If you pass it along, approximately how many other people usually see your copy of the HP Journal?

Write in a number \_

- 10. Please indicate the extent to which you use the HP Journal as a product information reference. (Circle one number)

- 1. Plays no role

- 2. An occasional reference

- 3. A frequent reference

- 4. A constant reference

- 11. Please indicate the extent to which you use the HP Journal as a source of technical information. (Circle one number)

- 1. Plays no role

- 2. An occasional reference

- 3. A frequent reference

- 4. A constant reference

12. Listed below are qualities that Hewlett-Packard strives to maintain. Please tell us to what extent the HP Journal supports these qualities.

(Circle one number per line)

| Qualities                   | Greatly<br>Reinforces | Somewhat<br>Reinforces | Has No<br>Effect | Tends to<br>Detract |

|-----------------------------|-----------------------|------------------------|------------------|---------------------|

| a. Product quality          | 1                     | 2                      | 3                | 4                   |

| b. Financial stability      | 1                     | 2                      | 3                | 4                   |

| c. Strong customer support  | 1                     | 2                      | 3                | 4                   |

| d. New product development  | 1                     | 2                      | 3                | 4                   |

| e. Reliable supplier        | 1                     | 2                      | 3                | 4                   |

| f. A broad line of products | 1                     | 2                      | 3                | 4                   |

| g. Technically advanced     | 1                     | 2                      | 3                | 4                   |

| h. Good company to work for | 1                     | 2                      | 3                | 4                   |

| i. Corporate citizenship    | 1                     | 2                      | 3                | 4                   |

|                             |                       |                        |                  |                     |

13. Now please rank these same qualities in the order of importance to you. (Write 1 next to the most important quality, 2 next to the second most important and so on. Please rank at least five.)

| a. | Product quality          |  |

|----|--------------------------|--|

| b. | Financial stability      |  |

| C. | Strong customer support  |  |

| d. | New product development  |  |

| e. | Reliable supplier        |  |

| f. | A broad line of products |  |

| g. | Technically advanced     |  |

| h. | Good company to work for |  |

| i. | Corporate citizenship    |  |

14. Of all the periodicals (magazines and trade journals) you read, please list those that are most important to you.

15. Please list other publications that you consider comparable to the HP Journal as sources of technical information.

| 16. | Please circle your area of specialty: |  |

|-----|---------------------------------------|--|

|     | (circle one number)                   |  |

- 1. Research

- 2. Development Engineering

- 3. Product Management

- 4. Project Management 5. Production

- 6. Marketing

- 7. General Management

- 8. Other

can use an external power supply. When the supply is connected to the external power input lines, its presence is detected automatically and an internal relay disconnects all logic except the microprocessor and a low-power clock buffer from the system under test. The relay actuates so that the external supply can absorb virtually all the extra load required by the exerciser. An additional advantage of this technique is that the exerciser can be used even when power supply margin tests are run on the product under test. The microprocessor always runs from the power supplies of the product being tested.

Protection circuits are built into the exerciser so that reverse voltage on the external supply will not actuate the

Non-Overlay Mode. Processor sees 32 identical  $2K \times 8$  ROM images.

Free-Run Mode. Processor sees 64K filled with NOP instructions.

Overlay Mode. Same as (a), except one address accesses 64K user space and one address accesses switch register.

#### During Overlay Mode:

(d)

Two addresses reserved for exerciser user

Fig. 5. 5001 A operating modes.

relay, thus protecting the exerciser from damage. An overvoltage protection circuit is also included. If overvoltage occurs, an internal power Zener diode will avalanche, blowing an internal fuse. This fuse is socketed for easy replacement. The fuse also provides overcurrent protection.

#### **Software Design**

The memory mapping scheme allows versatility in test location. The internal preprogrammed stimulus routines reside in a 2048×8 ROM. The decoding of this ROM allows the individual routines to appear to run in any of the thirtytwo 2K× 8 pages of memory. The ROM images itself into these pages by ignoring the five most-significant address lines in the ROM decoding. The result is that a stimulus program can be made to overlay any page in the memory space of the product under test. The user data bus processing circuit assures that data streams resulting from instruction fetch in the stimulus programs do not interfere with the interleaved data streams resulting from instruction execution (the stimulus).

The user data bus processing circuit represents an unusual, but effective, way to access data occurring simultaneously on two buses without resorting to an elaborate mapping or clocking scheme. The situation is one wherein two 64K address spaces are mapped into one that can be read by a conventional 16-bit-address-bus microprocessor. By mapping the user's addressable space into a single location, then overlaying that single location into the internal address space, great economy in hardware was achieved. Figs. 4, 5c, and 5d illustrate this overlay mode. The user data processing circuit captures the data at the end of an instruction cycle just as the microprocessor would. It latches the data on every machine cycle, and then presents the data to a four-level eight-bit-wide shift register. The output of this register is decoded as if it were a single address in the address space of the internal bus. The address chosen overlays a location that is very infrequently accessed by the internal programs. The location selected is the reset vector (note that a reset pulse will cause the ROM to be accessed instead of the shift register). Thus, to access any location in the user space the program simply reads from the location desired, and then reads the shift register output in the following instruction. The time delay introduced by the shift register is a function of the number of machine cycles required to read the register. The dual bus structure causes two sets of data to be present for every valid address: ROM or register data in the exerciser, and the product response in the user's data bus. The technique simply ignores the internal data and reads the delayed response from the user bus. The hardware overhead is only four packages, since timing and decoding signals are already present.

The microprocessor instruction set test represents a new departure in testing. The test is essentially a functional test of the instruction set. A sequence of instructions is executed that constantly checks the effect of instructions as they are executed. If at any point an instruction produces a faulty result, a branch is made to a "skip-chain" that terminates the program early, reducing the time interval of the test. Since the test is executed in a loop with signature analyzer start and stop timing emitted at the extremes of the loop, probing +5Vdc will produce a single measurement unique

to a given loop time (with 99.998% probability). The exercise is so constructed that tables in ROM are frequently used in computations, and a simulated stack is used for extensive branching and jump testing. The mapping feature of the ROM as described above is useful in this regard. The program tests all instructions except the WAIt-for-interrupt instruction. The program writes patterns to addresses that cannot be checked with the loop-length method so that a complete test result is obtained with probing of address and data bus lines during the test.

The test has another unusual feature: the real-time test of interrupts. With a stack simulated by tables in ROM, the program writes patterns to the control logic in the exerciser that cause interrupt lines on the processor to be toggled. Various tests of maskable and nonmaskable interrupts are performed, including the correctness of the transfer of control to the appropriate service routine. The fact that the interrupt lines to the user system are intercepted is essential for this test, as well as for the general stimulus programs. The microprocessor test is executed at the speed of normal operation by using the normal clocks and power supplies in the product under test, thereby performing a true kernel test in the product. The only drawback in this test is that fanout and timing tests are not made on the unit. However, the advantage that the actual microprocessor in the product is used should not be overlooked. A limitation of the input checking equipment approach, for example, is that the processor is emulated, rather than exercised.

Since the 6800 instruction set uses relative branching as a means of transfer of control within a program, positionindependent code can be written. Some internal preprogrammed stimulus programs can be relocated to appear to run in other address spaces because they are written with relative branches to do looping. The advantage of this approach is the flexibility gained as custom programs are developed.

An HP Model 5004A Signature Analyzer or 5005A Signature Multimeter can be used as a remote display. This feature, which can be useful in some applications, was implemented for the testing of the 5001A. Because the program can control the start and stop and clock of the signature analyzer, a clever programmer can "finesse" a signature into the display. This occurs if +5Vdc or all logic ones are clocked into the signature analyzer when a finesse-type program is running. If the programmer knows ahead of time the number of clocks required to produce the desired signatures, then a simple loop can be set up to produce the desired result. The initial application was such that the result of a functional test produced the finesse signature of PA55 which also could be easily interpreted as PASS. Other failures are identified by signatures of FA01, FA02, FA03, et cetera. These results represent failure at test 01 and so forth. The advantage here is that a functional test can detect a fault and isolate it to a functional block such as a particular printed circuit board before diagnostics are run for that failure. The 65,535 unique signatures available open a variety of possibilities.

#### **Product Design**

The 5001A case is injection-molded glass-filled polycarbonate. The case is designed to be used with a family of microprocessor exercisers. Hence, the model can be designated by providing a different front-panel overlay for each instrument in the family.

All the nonelectrical parts are made from polycarbonate: the case (two halves), the stimulus connector, the signature analyzer connector, and the overlay panel. The use of polycarbonate makes the instrument very durable and nonconductive, two important features in the environment where the 5001A is used.

#### **Acknowledgments**

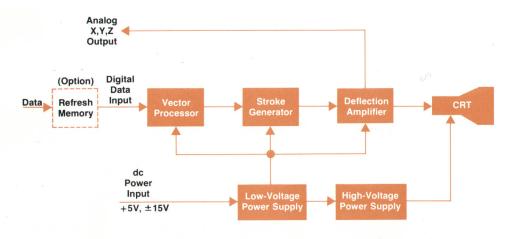

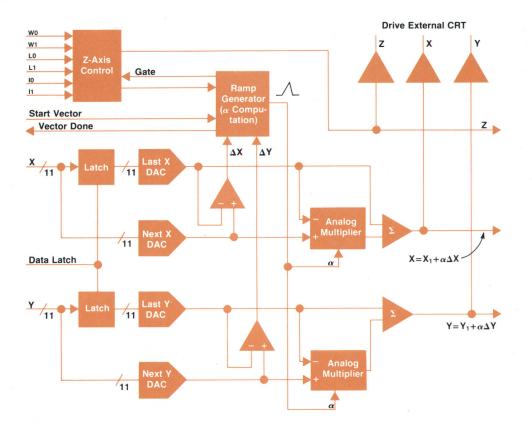

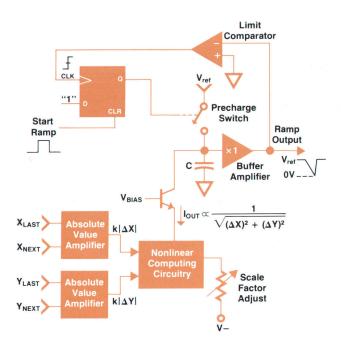

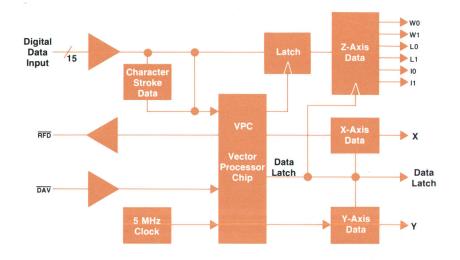

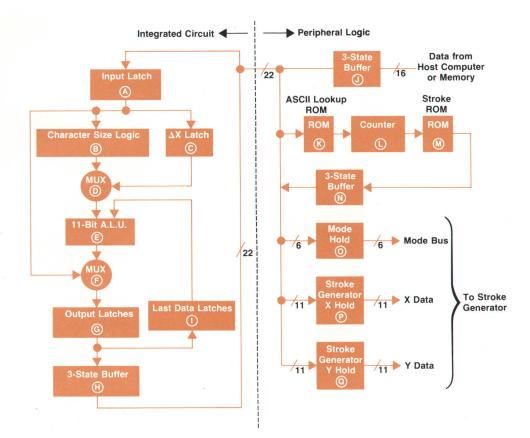

The author would like to thank Gary Gordon for his leadership and help in the early stages of the development. Gary proposed the first microprocessor stimulus product at the same time the author had implemented a similar test approach for the HP 2804A Quartz Digital Thermometer in another HP division. Andrew Stefanski contributed to the generalization of the external stimulus concept. Ken Mac-Leod contributed to the development with innovative suggestions and guidance, particularly with an internal design review process that was very effective.